Luke Lang Engineering Director at Cadence says that Just because you have a hard macro doesnt mean you need to define a macro model. Low Power Verification for Advanced Users.

Conformal Low Power Electronics Assignment Help And Homework Help Conformal Low Power Project Help

The RAKs are kept up-to-date with the current release of the software and based on customer feedback.

. Power gating logic isolation state retention and clock gating are. Designs are using new methodologies and design techniques to reduce the leakage current. A necessary condition for the f -conformal equivalence of.

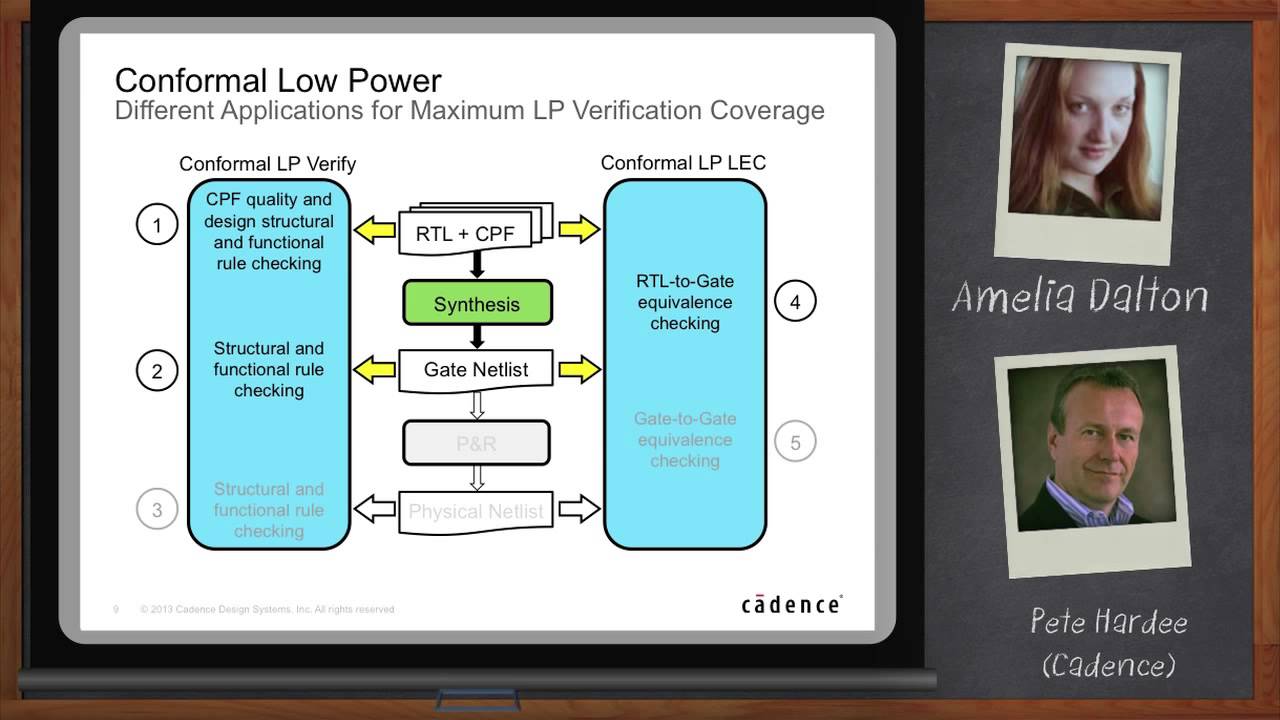

You could have explicit power pins and implicit net sets and net expressions defined in parallel. Download Free Conformal Lec User Manual tutorial describes how to formally verify that the synthesized design is. Conformal low power enables designers to create power intent then verify and debug multi-million-gate designs without simulating test vectors.

Low power design techniques As designs are moving towards smaller and smaller technologies 90nm 65nm leakage current has become significant and contributes to overall power. Encounter Conformal Low Power enables designers to create power intent then verify and debug multimillion-gate designs optimized for low power without simulating test vectors. Any LP cell if not specified with define_ command but found in library and in design will not be considered as.

Custom IP blocks and analog macros often contain low-power features. The design was implemented in the Cadence. Cadence Conformal.

The theory of statistical manifolds wrt. The kit includes overviews tutorials with demo design instructions are provided on how to set up uthe ser environment and provides introductions for the advanced features of Conformal Low Power --. Cadence customers can learn more in a Rapid Adoption Kit RAK titled Conformal Low Power and RTL Compiler.

Incorrect power and ground connec-tivity including shorts and opens Instances with undefined power domains or mixed power domains Missing redundant and incorrect. The VLSI design cycle is divided into two phases. A macro model is not necessary Luke further elaborates.

The IBM-Chartered 90nm Low Power Reference Flow was developed using the IBM 90nm CMS9FLP process information for the ARM Artisan Metro low-power libraries and highlights the low-power features of the Cadence Encounter digital integrated circuit IC platform. -manifolds is found extending that for the. Conformal low power enables designers to create power intent then verify and debug multi-million-gate designs without simulating test vectors.

What Is The Low-Power Coalition. Urethane Polyurethane Resin UR Urethane conformal coatings are known for their excellent moisture and chemical resistance. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use.

CPF will update or create the net sets and expressions. Conformal Low Power reports. All of the power and ground nets PG nets in your design should have the signal type Power or Ground.

VC LP can be run at RTL post-synthesis and post-PR and can catch low power bugs earlier and faster than traditional methods. Team FED. To Conformal Low Powerit analyzes the design with real power connectivity not assumed connectivity based on instance name.

NXP Proof Point Project Using CPF Based Low Power Solution Power Forward low-power platform SoC results CPF-based functional SoC consists of 11 islands verification using simulation 3 major power consumers -RISC catches system level power CPU VLIW DSP L2 System issues early in the flow Cache are controlled using DVFS Use of CPF ensured what. Flow-based solutions Standards to promote integration of open technologies into cohesive flows CPF was contributed to LPC 4Q06 approved as Si2 standard in March 2007 CPF is fully open to the entire industry at no cost anyone can influence direction Analyze develop semantic consistency across data exchanges User. Cadence Conformal EC enables designers to verify the widest variety of circuits including complex arithmetic logic datapaths memories and custom logic.

Conformal Lec User Manual Conformal Smart LEC Author. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use. Closed loop verification methodology using Conformal Low Power Below is a complete list of the current RAKs that are available to Cadence customers.

As designs continue to get more complicated in order to meet aggressive requirements for power performance area and time to market the formal verification of the designs continues to be a staple and must-have signoff metric to ensure silicon success. Offering key technologies of massive parallelism and adaptive proof Conformal Smart LEC improves runtime by an average of 4X compared to existing solutions with the same compute resources. New conformal invariant tools are defined.

Low power design techniques add new design elements at different stages of the design flow. Front-end covers the architectural specifications coding and verification whereas back-end involves the physical implementation of the design on the targeted technology node. A conformal structure is reviewed in a creative manner and developed.

Cadence Conformal Smart LEC is the next-generation equivalence checking solution. Liberty attributes for Lowpower are not considered by Conformal. They are both abrasion-resistant and solvent-resistant which results in coatings.

A consistent power intent for the analog and digital parts of your design is required. If you didnt know Conformals very own AE team put together some cool training materials for their customers based on large demand to help both new and intermediate users. Formal verification-driven equivalence low-power and ECO solutions.

You may have even worked with them in the past. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use. Read library -liberty lib command only identify the cells and maps to cells under define_ commands.

Already proven in thousands of tapeouts Conformal EC is the industrys most widely supported independent equivalence checking product. Architectural design bugs that violate the principles of low power design may exist even at RTL. Konform LED is a silicone conformal coating that is optically clear so it can be applied directly over LEDs without causing a reduction in light intensity or color shift.

This paper presents why LEC Logical Equivalence Check is important in the ASIC design cycle how to check it and. And its personal with Clay and Bruce. A single-domain hard macro without any low power component should be black-boxed.

Cadence Low Power Solution RTL to GDSII Low Power Design Cadence PiTP 2015 - Introduction to Topological and Conformal Field Theory 1 of 2 - Robbert.

Low Power Design And Verification

Low Power Design And Verification

Low Power Design And Verification

Cadence Low Power Solution Rtl To Gdsii Low Power Design Cadence Youtube

0 comments

Post a Comment